FAU-Team entwickelt Supercomputer-on-a-Chip

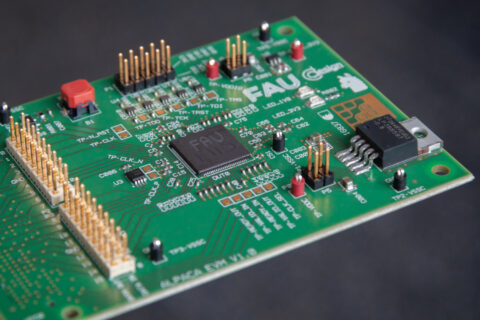

Ein Team des Lehrstuhls für Informatik 12 (Hardware-Software-Co-Design) von ESI-Sprecher Prof. Dr.-Ing. Jürgen Teich hat einen Chip entworfen, der 64 selbstentwickelte Rechenkerne integriert.

Der Chip namens ALPACA entfaltet eine enorme Rechenleistung von bis zu 384 Milliarden Rechenoperationen pro Sekunde bei einer elektrischen Leistungsaufnahme von weniger als 3 W.

Die Anwendungsgebiete von ALPACA sind vielfältig. Der Chip eignet sich besonders für die schnelle Verarbeitung von digitalen Signalen (Audio, Video) sowie von großen Datenmengen im Bereich des maschinellen Lernens und des wissenschaftlichen Rechnens. Durch den niedrigen Energiebedarf profitieren insbesondere Anwendungen aus Bereichen der Medizintechnik, IoT-Systeme und im Automobil.

Der Chip mit einer Fläche von gerade einmal 10 mm2 wurde im Rahmen des Sonderforschungsbereich/Transregio 89 „Invasives Rechnen“ der Deutschen Forschungsgemeinschaft (DFG) entwickelt und in der Halbleitertechnologie 22 nm gefertigt. Ein Chip alleine liefert aber noch keine Beschleunigung, wenn es nicht geeignete Übersetzungswerkzeuge zu dessen Programmierung gäbe. In einem einzigartigem Hardware-Software-Co-Design ist daher parallel zu dem eigentlichen Chipentwurf ein leistungsfähiger Compiler zur Parallelisierung und automatischer Abbildung von Schleifenprogrammen entstanden.

PD Dr.-Ing. Frank Hannig

Department Informatik (INF)

Lehrstuhl für Informatik 12 (Hardware-Software-Co-Design)

- Telefon: +49 9131 85-25153

- E-Mail: frank.hannig@fau.de